- 您现在的位置:买卖IC网 > Sheet目录369 > W9725G6KB-25I (Winbond Electronics)IC DDR2 SDRAM 256MBIT 84WBGA

�� �

�

�

�W9725G6KB�

�8.2.2.2�

�DLL� Enable/Disable�

�The� DLL� must� be� enabled� for� normal� operation.� DLL� enable� is� required� during� power-up� initialization,�

�and� upon� returning� to� normal� operation� after� having� the� DLL� disabled.� The� DLL� is� automatically�

�disabled� when� entering� Self� Refresh� operation� and� is� automatically� re-enabled� and� reset� upon� exit� of�

�Self� Refresh� operation.� Any� time� the� DLL� is� enabled� (and� subsequently� reset),� 200� clock� cycles� must�

�occur� before� a� Read� command� can� be� issued� to� allow� time� for� the� internal� clock� to� be� synchronized�

�with� the� external� clock.� Failing� to� wait� for� synchronization� to� occur� may� result� in� a� violation� of� the� t� AC�

�or� t� DQSCK� parameters.�

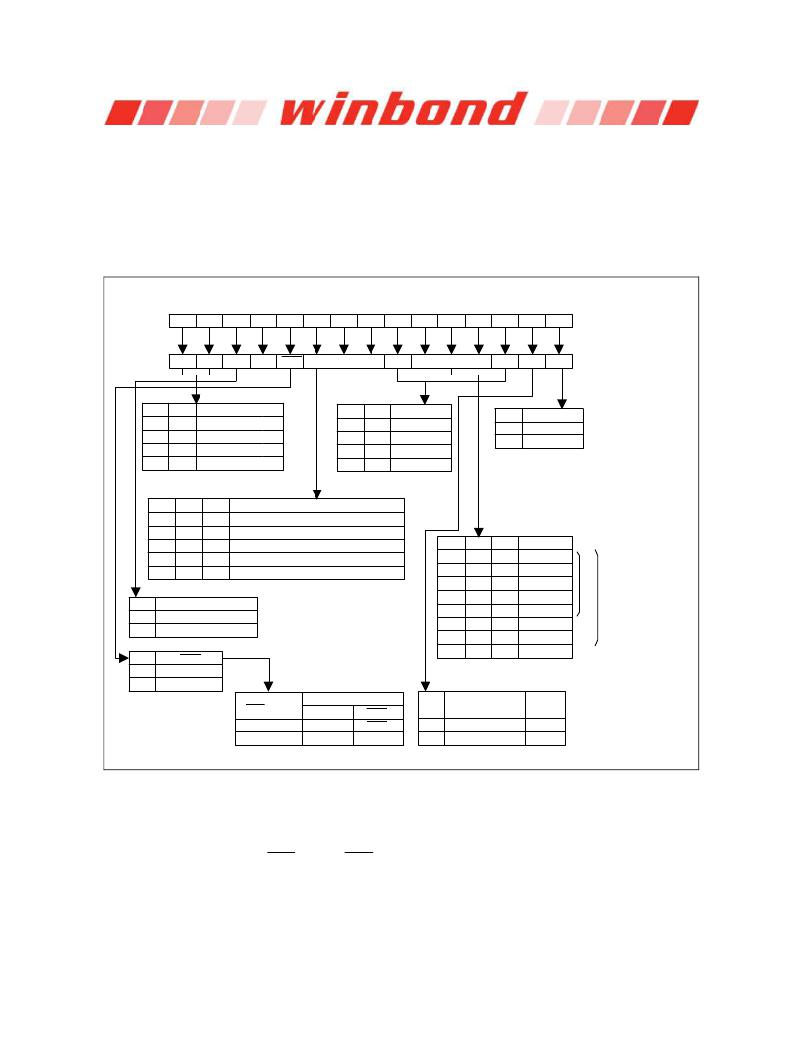

�BA1�

�BA0�

�A12�

�A11� A10�

�A9�

�A8�

�A7�

�A6�

�A5�

�A4�

�A3�

�A2�

�A1�

�A0�

�Address� Field�

�0�

�1�

�Qoff�

�0*� 1� DQS�

�OCD� program�

�Rtt�

�BT�

�Additive� WR� Latency�

�Rtt�

�D.I.C� DLL�

�Extended� Mode� Register� (1)�

�BA1�

�0�

�0�

�1�

�1�

�BA0�

�0�

�1�

�0�

�1�

�MRS� mode�

�MR�

�EMR� (1)�

�EMR� (2)�

�EMR� (3)�

�A6�

�0�

�0�

�1�

�1�

�A2�

�0�

�1�

�0�

�1�

�Rtt� (nominal)�

�ODT� Disabled�

�75� ohm�

�150� ohm�

�50� ohm*� 2�

�A0�

�0�

�1�

�DLL� Enable�

�Enable�

�Disable�

�Driver� impedance� adjustment�

�A9�

�0�

�A8�

�0�

�A7�

�0�

�OCD� Calibration� Program�

�OCD� calibration� mode� exit;� matain� setting�

�0�

�0�

�1�

�Drive� (1)�

�Additive� Latency�

�0�

�1�

�1�

�1�

�0�

�1�

�0�

�0�

�1�

�Drive� (0)�

�Adjust� mode*� 3�

�OCD� Calibration� default*� 4�

�A5�

�0�

�0�

�A4�

�0�

�0�

�A3�

�0�

�1�

�Latency�

�0�

�1�

�0�

�1�

�0�

�2�

�A12�

�0�

�1�

�A10�

�Qoff� (Optional)*� 5�

�Output� buffer� enabled�

�Output� buffer� disabled�

�DQS�

�0�

�1�

�1�

�1�

�1�

�1�

�0�

�0�

�1�

�1�

�1�

�0�

�1�

�0�

�1�

�3�

�4�

�5�

�6�

�Reserved�

�0�

�Enable�

�1�

�Disable�

�Output� Driver� Impedance� Control�

�A10�

�(DQS� Enable)�

�Strobe� Function� Matrix�

�DQS� DQS�

�A1�

�Output� driver�

�impedance� control�

�Driver�

�size�

�0� (Enable)�

�1� (Disable)�

�DQS�

�DQS�

�DQS�

�Hi-z�

�0�

�1�

�Normal�

�Reduced�

�100%�

�60%�

�Notes:�

�1.� A11� default� is� “� 0� ”� RDQS� disabled.�

�2.� Optional� for� DDR2-667,� mandatory� for� DDR2-800� and� DDR2-1066.�

�3.� When� Adjust� mode� is� issued,� AL� from� previously� set� value� must� be� applied.�

�4.� After� setting� to� default,� OCD� calibration� mode� needs� to� be� exited� by� setting� A9-A7� to� 000.� Refer� to� the� section� 8.2.3� for�

�detailed� information.�

�5.� Output� disabled� -� DQs,� LDQS,� LDQS� ,� UDQS,� UDQS� .� This� feature� is� used� in� conjunction� with� DIMM� I� DD� measurements�

�when� I� DDQ� is� not� desired� to� be� included.�

�Figure� 3� –� EMR� (1)�

�Publication� Release� Date:� Sep.� 03,� 2012�

�-� 12� -�

�Revision� A03�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

W972GG6JB-3I

IC DDR2 SDRAM 2GBITS 84WBGA

W9751G6IB-25

IC DDR2-800 SDRAM 512MB 84-WBGA

W9751G6KB-25

IC DDR2 SDRAM 512MBIT 84WBGA

W9812G6JH-6I

IC SDRAM 128MBIT 54TSOPII

W9816G6IH-6I

IC SDRAM 16MBIT 50TSOPII

W9825G6JH-6I

IC SDRAM 256MBIT 54TSOPII

W9864G6JH-6I

IC SDRAM 64MBIT 54TSOPII

WM-5614

CABINET WALL MOUNT 37.25X17.9"

相关代理商/技术参数

W9725G6KB25I TR

制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X16, IND TEMP

W9725G6KB25K

制造商:WINBOND 制造商全称:Winbond 功能描述:DLL aligns DQ and DQS transitions with clock, Data masks (DM) for write data, Write Data Mask

W9725G6KB-3

制造商:WINBOND 制造商全称:Winbond 功能描述:DLL aligns DQ and DQS transitions with clock, Data masks (DM) for write data, Write Data Mask

W9725G8JB

制造商:WINBOND 制造商全称:Winbond 功能描述:8M ? 4 BANKS ? 8 BIT DDR2 SDRAM

W9725G8JB25

制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR2 SDRAM 256M-Bit 32Mx8 1.8V 60-Pin WBGA

W9725G8JB25I

制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR2 SDRAM 256M-Bit 32Mx8 1.8V 60-Pin WBGA

W9725G8JB25ITR

制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8, IND TEMP

W9725G8JB25TR

制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8